# Diseño de un sistema de comunicación de voz usando DC-PLC basado en modulación BFSK

Wagner Gómez, Yosbel J. Herrera Fonseca, Ismael Lavandera Rodríguez, Enrique Ernesto Valdés Zaldívar.

#### RESUMEN

En este trabajo se abordan los conceptos fundamentales en el diseño de un sistema de comunicaciones de voz utilizando los principios de funcionamiento de las comunicaciones por línea de potencia de corriente de directa (DC-PLC: Direct Current - Power Line Communications) basado en una modulación BFSK. El sistema se compone de un subsistema de transmisión y de un subsistema para la recepción de la señal de voz, estos elementos se interconectan entre sí a través de un canal de DC-PLC referido a un par trenzado de cobre. El subsistema de transmisión realiza las funciones asociadas al acondicionamiento, la digitalización, y el procesamiento de la señal para su transferencia digital con una modulación BFSK en el canal de comunicación. En el subsistema de recepción se lleva a cabo la demodulación BFSK, el procesamiento y la recuperación nuevamente de la señal de voz para su supervisión. Se propone para ambos subsistemas un diseño basado en el empleo de microcontroladores con núcleo 8051 de la familia Silicon Laboratories. El periférico UART disponible en los microcontroladores 8051 se emplea para la transferencia de los datos digitales y es aplicable como método de transmisión en el tipo de canal DC-PLC. Además, se presentan y exponen los criterios de diseño de los circuitos internos a través de sus esquemas eléctricos.

Palabras claves: Voz, DC-PLC, modulación BFSK, microcontroladores 8051.

#### **ABSTRACT**

This work addresses the fundamental concepts in the design of a voice communications system that uses the operating principles of direct current power line communications (DC-PLC: Direct Current - Power Line Communications) based on BFSK modulation. The system is composed of a transmission subsystem and a voice signal reception subsystem, these elements are interconnected through a DC-PLC channel referenced to a twisted copper pair. The transmission subsystem performs the functions associated with the conditioning, digitization and processing of the signal for its digital transfer with a BFSK modulation in the communication channel. The receiving subsystem performs the BFSK demodulation, processing and recovery of the voice signal for monitoring. For both subsystems a design based on the use of Silicon Laboratories 8051 core microcontrollers is proposed. The UART peripheral available in the 8051 microcontrollers is used for digital data transfer and is applicable as a transmission method in the DC-PLC channel type. In addition, the design criteria of the internal circuits are presented and exposed through their electrical schematics.

Keywords: Voice, DC-PLC, BFSK modulation, 8051's microcontroller

Design of a voice communication system using DC-PLC based on BFSK modulation.

Recibido: 11/2022 Aceptado: 03/2023

#### 1. -Introducción

Los avances tecnológicos de las comunicaciones y la microelectrónica han posibilitado que la transferencia de datos por un canal de comunicación se logre de forma eficiente a través de medios de transmisión alámbricos e inalámbricos. Se denominan como medios transmisión inalámbricos, el aire, el vacío o el agua. En el caso de los medios de transmisión alámbricos, se proporciona un camino físico o línea de transmisión; entre los que se destacan están el cable coaxial, la fibra óptica y el par de cobre. En el caso de los medios de transmisión alámbricos, el par de cobre se caracteriza por su capacidad de transmisión en términos de velocidad o de ancho de banda, dependiendo drásticamente de la longitud de la línea y si el tipo de enlace, es punto a punto o multipunto.

La capacidad proporcionada por el par de cobre para entregar potencia eléctrica y simultáneamente lograr transmisiones de datos, solo se refiere a las comunicaciones por línea de potencia (PLC: Power Line Communication), y sobre esta tecnología se han dado muchas consideraciones durante los últimos 20 años [1]. Típicamente, las comunicaciones por línea de potencia pueden categorizarse en dos tipos: comunicaciones por línea de potencia de corriente de directa (DC-PLC: Direct Current - Power Line Communication), y comunicaciones por línea de potencia de corriente alterna (AC-PLC: Altern Current Power Line Communication). En la actualidad la mayoría de los investigadores se enfocan en proporcionar soluciones para AC-PLC, no obstante, la DC-PLC también tiene múltiples aplicaciones [2]. Se evidencian estas aplicaciones en los campos destinados a la generación de energía renovable distribuida, a la industria del transporte (automovilismo, ferroviario y aeronáutico), a sistemas de redes de sensores alimentados por corriente de directa, entre otros. En la literatura especializada solo se refieren investigaciones asociadas a la transmisión de datos, voz, video y soporte de servicios de internet sobre las redes AC-PLC, en el caso de las redes DC-PLC solo se limitan fundamentalmente al uso de transferencias de datos de baja latencia [3,4].

El rendimiento de la tecnología DC-PLC depende principalmente de la atenuación de la línea de potencia, los ruidos impulsivos y la interferencia entre símbolos en los cables largos. Para mitigar estas dificultades se aplican protocolos de comunicación en el proceso de transmisión de datos, tales como: El CAN, LIN, UART y RS232/485, todos comúnmente son usados en múltiples aplicaciones. Los desarrolladores actuales reportan soluciones que presentan como capa física de estos protocolos la tecnología DC-PLC [5]. En esta investigación se emplea, precisamente, el protocolo UART para llevar a cabo la transferencia de datos sobre un canal de DC-PLC.

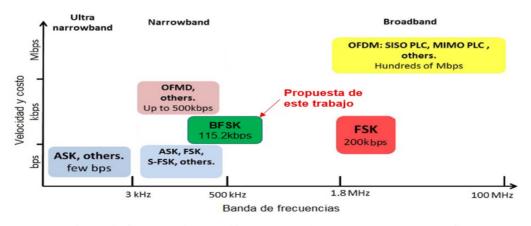

Por otro lado, atendiendo al tipo de aplicación de las tecnologías PLC existen múltiples variantes a utilizar: La PLC de banda estrecha (NB-PLC: Narrow Band-PLC), y la PLC de banda ancha (BB-PLC: Broad Band-PLC) [6]. Esta última variante alcanza velocidades de datos superiores a 1 Mbps usando modulación de división de frecuencias ortogonales (OFDM: Orthogonal Frequency Division Modulation) en bandas de frecuencias por encima de los 1.8 MHz. Para los sistemas NB-PLC las velocidades alcanzan hasta los 200 kbps, con la utilización de varios tipos de modulaciones en frecuencia y fase, se destaca por su bajo costo la modulación de desplazamiento de frecuencia binaria (BFSK: Binary Frequency Shift Keying) obteniéndose tasa de datos de pocos kbps en el rango de frecuencia hasta los 500 kHz [3]. En el documento [1], se recoge en una tabla comparativa los estándares existentes asociados a la tecnología PLC atendiendo a su esquema de modulación, ancho de banda, banda de frecuencia y velocidades de datos. Se evidencia en el estándar STM7580 que la modulación BFSK solo se utiliza en aplicaciones NB-PLC, en el rango de frecuencia de 60 a 132.5 kHz, y con velocidades de datos hasta 4.8 kbps[1].

El autor Debita en su artículo, "BPL-PLC Voice Communication System for the Oil and Mining Industry" [7], realiza un análisis de aplicaciones de sistemas de comunicación de voz de alta eficiencia basados en la tecnología BB-PLC en redes de voltaje medio de corriente alterna, incluyendo ambientes hostiles sobre áreas como la industria minera y petrolera. En este documento afirma la bondad de tener ya una infraestructura de energía hecha, la cual se puede emplear en caso de emergencia como canal de comunicación entre los rescatistas y el personal atrapado. Varios modelos fueron considerados, así como los tipos de acoplamientos y las dimensiones de los paquetes de datos a enviar. Se concluye afirmando el resultado de la aplicabilidad de esta tecnología de comunicaciones en el campo de la industria minera y petrolera.

El autor Zaqout en su artículo, "VoIP Using Power Line Communication" [3], estudia la garantía de enviar información de voz usando VoIP sobre tecnologías PLC en corriente alterna o corriente directa. Pero solo realiza cinco experimentos de estudio en redes del hogar para medir la eficiencia de su propuesta para transferencia de información de banda ancha, discute aspectos fundamentales de la tecnología IP sobre BB-PLC y los protocolos IP-PBX y SIP. Concluye que esta infraestructura de BB-PLC sirve como punto de acceso para transferencia de datos, llamadas de voz, llamadas de video y servicio de internet y propone enfocarse en trabajos futuros en la red pública de abonado (PTSN).

En el caso de los autores Ganiyu Adedayo Ajenikoko y Ezekiel Olusegun Ojekunle, en su artículo "Investigative study of voice and data Communication over Powerline Communication System" [8], realizan también un análisis de la efectividad de usar trasmisiones de voz y datos sobre BB-PLC en líneas de alimentación de corriente alterna. Enfocan el uso como tecnología

de última milla en lugares rulares donde no llega el par de cobre, la fibra óptica ni el Wi-Fi. Presentan una vista sobre los equipamientos, métodos de comunicación, aplicaciones y retos para la implementación de estos sistemas.

En el artículo "High-speed Audio Communications in Domestic Power Line Channels" [9], por los autores Apaza Mamani y Zenteno Bolaños, se hace una propuesta de diseño de un transceptor de bajo costo para comunicaciones de audio. Se explica en este trabajo las mediciones de los ruidos e interferencias asociados al canal PLC en su uso doméstico en líneas de alimentación de corriente alterna. Su diseño se basa en el empleo de FSK para transmisiones de datos de BB-PLC con tasa de 200 kbps en el rango de frecuencia superior a los 1.6 MHz.

De acuerdo a la revisión de estas publicaciones se evidencia que la mayoría de las aplicaciones de comunicaciones de audio son soportadas en líneas de corriente alterna con un esquema de banda ancha. Por ende, las transmisiones de datos se establecen en los rangos de frecuencias por encima de 1.6 MHz y se afectan considerablemente, en cuanto a la atenuación, por la respuesta de frecuencia que presenta el canal PLC.

Para NB-PLC se ha encontrado propuestas de comunicación con un costo de implementación de \$2 dólares donde transmiten 5 bps utilizando modulaciones como ASK (Amplitude-shift keying) o FSK (Frequency-shift keying). Para mayores velocidades utilizan OFDM (Orthogonal Frequency Division Multiplexing), para ésta última implementación de moduladores OFDM (a conocimiento del autor) no se reportan costos en la literatura [9]. Para BB-PLC se ha implementado soluciones de diseño de bajo costo que emplea la modulación FSK en líneas de corriente de alterna para alcanzar velocidades de datos hasta 200 kbps [9].

En comparación con la modulación OFDM, la modulación BFSK resulta más sencilla y de bajo costo de implementación, esta cumple con los requerimientos de ancho de banda para la transferencia de la señal de voz. Además, su rendimiento para la transmisión de dicha señal es eficiente ante la interferencia de diferentes fuentes de ruidos (impulsivos, gaussianos, blanco, y de banda estrecha) en sistemas que utilicen la tecnología DC-PLC. En adición a esto, se establecen requerimientos al sistema en cuestión, de tal manera que sea de bajo consumo y de dimensiones pequeñas y limitado en potencia, por tanto, se propone para esta investigación el esquema de modulación BFSK aplicada en NB-PLC.

La presente investigación tiene como objeto de estudio la aplicación de la modulación BFSK en la tecnología DC-PLC de banda estrecha, y su objetivo es diseñar un sistema de comunicación que permita la transmisión digital de la señal de voz a distancias medias sobre una línea de potencia de corriente de directa. De acuerdo a la literatura consultada en relación a esta temática, no se reporta ampliamente la utilización de esta modulación en aplicaciones de NB-PLC con tasas de datos por encima de los 4.8 kbps. Las contribuciones científicas de esta investigación son sustentadas fundamentalmente en alcanzar una velocidad de datos superior a los 4.8 kbps con una propuesta de diseño de un sistema NB-PLC con modulación BFSK en el orden de 115,2 kbps, y que permita la transferencia digital de la señal de voz utilizando una línea de potencia de corriente directa, véase la figura 1.

Figura 1: Comparación de diferentes soluciones en el desarrollo PLC.

El artículo se encuentra organizado en seis secciones. En la sección 2 se presenta la concepción general del sistema completo y se exponen las funciones que realizan el subsistema de transmisión y recepción de información. En la sección 3 se abordan los criterios de diseño que se consideraron para acometer el diseño del subsistema de transmisión, y se explican detalladamente los componentes que lo constituyen a través de sus esquemas eléctrico. De igual forma, en el apartado 4 se tratan los principios

de diseño del subsistema de recepción y los diagramas eléctricos de sus bloques internos. En la sección 5 se abordan los resultados obtenidos de los principales circuitos y en el apartado seis las conclusiones del artículo.

## 2.- CONCEPCIÓN DE DISEÑO DEL SISTEMA PROPUESTO

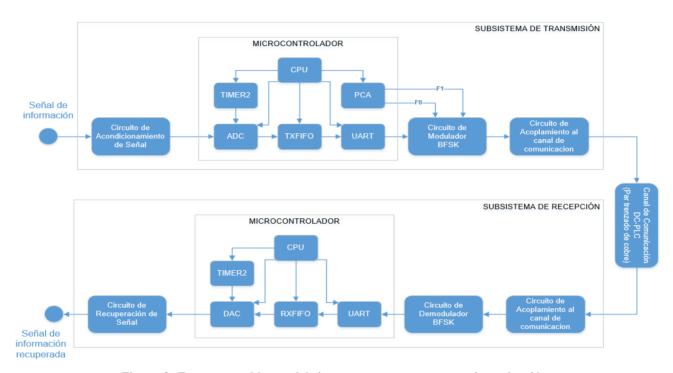

La concepción de diseño del sistema propuesto se compone de forma general por un subsistema de transmisión y un subsistema de recepción de información, los cuales se interconectan a través de un canal comunicación, que en este caso se refiere a un canal DC-PLC de dos hilos constituido por un par trenzado de cobre, como se muestra en la figura 2. El diseño de ambos subsistemas se basa en el empleo de microcontroladores con núcleo 8051 de la familia Silicon-Laboratories. El software de cada microcontrolador se implementa en el lenguaje C usando la herramienta profesional de desarrollo Keil µVision5.

Figura 2: Esquema en bloque del sistema propuesto para esta investigación.

El subsistema de transmisión realiza las funciones correspondientes al acondicionamiento, la adquisición, la digitalización y el procesamiento de la señal de información (que comprende las señales de voz de bajas frecuencias dadas en el rango 300 Hz a 3200 Hz) para su transmisión digital por medio de un canal de dos hilos. Para ello, se dispone de un microcontrolador con un puerto serie UART, y se incorpora un modulador BFSK, con su circuito de acoplamiento al canal de comunicación. En el epígrafe 3 se abordará con más detalles los criterios de diseño que se consideraron para su implementación.

El subsistema de recepción lleva a cabo las funciones relacionadas a la amplificación, filtrado, demodulación de la señal transmitida con modulación BFSK a través del canal de comunicación. Por tanto, se incluye un circuito de acoplamiento al canal de comunicación y un demodulador BFSK que entrega la señal digital de información en banda base a un bloque microcontrolador a través del puerto serie UART. Este permite la recepción digital de la señal transmitida para el procesamiento y recuperación de la señal de información a su naturaleza analógica. Además, se encarga de la tele alimentación del subsistema de transmisión por medio de los dos hilos. En el epígrafe 4, se tratará con más profundidad los aspectos del diseño.

El canal de comunicación, el par trenzado de cobre, presenta un comportamiento de respuesta de frecuencia similar a un filtro pasa-bajo. La respuesta transferencial del canal de comunicación PLC impone grandes retos asociados a la atenuación de las señales portadoras de información que influyen en factibilidad y rendimiento del sistema de comunicación [10]. Esto implica que existan ruidos asociados a componentes de muy bajas frecuencias en el canal de comunicación, y contribuyan a la degradación sustancial de la señal digital enviada por el subsistema de transmisión. Diferentes fuentes de ruidos afectan en

los sistemas PLC, los cuales se clasifican en ruido de banda estrecha, ruido de fondo y ruido impulsivo [11]. Por otro lado, los niveles de atenuación de la respuesta de frecuencia del canal por encima de 1 MHz son elevados, y por tanto la transmisión de la información usando la portadora BFSK por el canal se afecta considerablemente para las altas frecuencias.

Para llevar a cabo el diseño de ambos subsistemas de transmisión y recepción se consideraron los siguientes requerimientos técnicos:

- La alimentación de ambos subsistemas debe ser de 12 V. El subsistema de transmisión debe alimentarse a través de los dos hilos desde subsistema de recepción.

- El ancho de banda de las señales de bajas frecuencias a transmitir se encuentra entre los 300 Hz hasta 3200 Hz.

- La modulación seleccionada es la BFSK.

- El ancho de banda de transmisión de datos debe ser de 64 kbps.

- Los microcontroladores seleccionados son de la familia SiLabs.

- Distancia máxima del canal de comunicación debe ser de 50 m.

#### 3.- DISEÑO DEL SUBSISTEMA DE TRANSMISIÓN

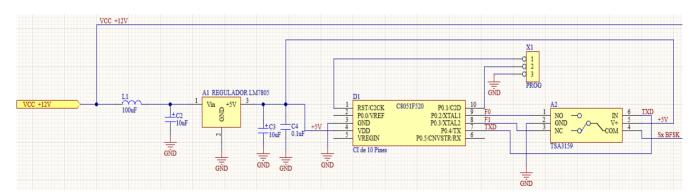

A partir de las funciones asociadas al subsistema de transmisión (S-TX) y teniendo en cuenta los requerimientos técnicos mencionados anteriormente, se lleva a cabo la selección de los componentes necesarios para acometer su diseño. A continuación, se enumeran los componentes fundamentales que se utilizan.

- Circuito integrado regulador de voltaje a 5V, LM7805.

- Microcontrolador de la familia SiLabs, C8051F520 (incorpora un núcleo compatible 8051 con otros periféricos analógicos y digitales).

- Circuito integrado de TEXAS INSTRUMENTS, TS5A3159A (constituye un conmutador analógico simple-polo doble-tiro).

- Circuito integrado del MAXIM, MAX7404 (que incluye un filtro pasa-bajo de orden 8 con capacitores-conmutados)

- Circuito integrado de ANALOG DEVICE, AD8062 (que incluye dos amplificadores operacionales de alta frecuencia)

- Componentes de misceláneas, relacionados a resistores, transistores, capacitores e inductores.

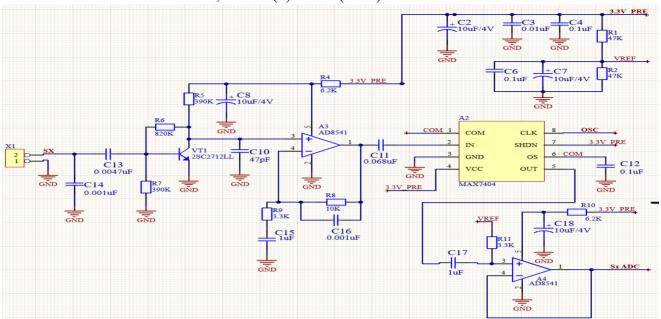

#### 3.1.- CIRCUITO DE ACONDICIONAMIENTO DE SEÑAL

El diseño del subsistema de transmisión presenta como primer bloque el circuito de acondicionamiento de señal. Este se encarga de amplificar y adecuar las señales de bajas frecuencias a los niveles de voltajes necesarios para su digitalización en todo el margen dinámico que dispone el conversor análogo-digital. Además, se implementa un filtro pasa-banda con la respuesta de frecuencia de la señal de información de 300 Hz a 3200 Hz para garantizar la eliminación de frecuencias indeseadas fuera de este rango. Para mejorar la cifra de ruido del subsistema de transmisión, se incorpora una etapa de amplificación inicial de la señal de información usando un transistor 2SC2712LL de bajo ruido, como se muestra en la figura 3. Se le incorpora una segunda etapa de ganancia, usando el amplificador operacional AD8541. La señal amplificada se pasa a través del filtro pasa-bajo de orden 8 con el circuito integrado MAX7404, a este se le establece una frecuencia de corte en 3800 Hz por medio de la señal de reloj OSC, que se proporciona por el bloque microcontrolador, para lograr la respuesta de frecuencia deseada. La salida del filtro pasa-bajo se ajusta un nivel de directa de la mitad de voltaje de alimentación del conversor utilizando una etapa de seguidor de voltaje con el amplificador operacional AD8541 para adecuar la señal de información al conversor análogo-digital (ADC, por sus siglas en inglés). Véase figura 3.

Figura 3: Esquema eléctrico del circuito de acondicionamiento de señal del subsistema de transmisión.

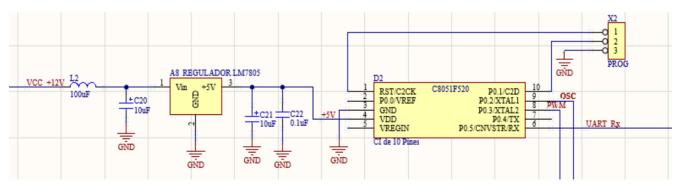

#### 3.2.- DISEÑO DEL BLOQUE MICROCONTROLADOR DEL S-TX

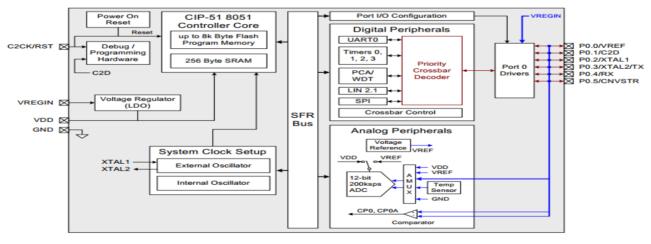

El bloque microcontrolador del S-TX tiene la función principal de realizar el procesamiento y control digital de la señal de información para su transmisión por el canal de comunicación. Para el diseño de este bloque se emplea el circuito integrado del fabricante SiLabs C8051F520, el cual presenta los recursos internos que se ilustran en el diagrama en bloque de la figura 4.

Figura 4: Diagrama en bloque del microcontrolador del SiLabs C8051F520 [12].

El procesamiento de la señal se inicia por el conversor análogo-digital (bloque ADC del subsistema de transmisión) que presenta el microcontrolador C80151F520. Este se encarga de digitalizar la señal de información a una frecuencia de muestreo de 8 kHz y una resolución de 8 bits, para obtener así un flujo de datos de 64 kbps. La frecuencia de muestreo se elige teniendo en cuenta el teorema de Nyquist, para eliminar el fenómeno de aliasing dado por el proceso de digitalización. También se dispone y configura un temporizador interno del microcontrolador (bloque TIMER 2) para establecer el tiempo de inicio de conversión del ADC a la frecuencia de muestreo seleccionada.

El flujo digital obtenido del bloque ADC se inserta en un búfer de transmisión de tipo FIFO (siglas de inglés First In First Out) (bloque TXFIFO), que sirve para almacenar las muestras correspondientes a la señal de información. Cuando el búfer

llega al límite de almacenamiento se activa una bandera y se conforma una trama de datos con la estructura que se muestra en la figura 5. Dicha trama se envía por un puerto serie asincrónico (bloque UART), el cual se configura a 8 bits de datos, sin paridad, a una tasa de transferencia de 115200 baudios por segundos para la evacuación de los datos sin pérdidas.

Figura 5: Estructura de la trama de datos del subsistema de transmisión.

Por otro lado, se utiliza el periférico asociado al Arreglo de Contadores Programables (PCA por sus siglas en inglés) que incluye el microcontrolador C8051F520 (bloque PCA), para la generación de las señales de frecuencias para la transmisión del bit '0' y bit '1', denominadas como "F0" y "F1" en la figura 2. Estas dos señales son usadas por el circuito modulador BFSK para efectuar la transmisión de la señal digital por el canal de comunicación. También, se emplea otro módulo del PCA para proporcionar el reloj de la frecuencia de corte al filtro pasa-bajo del circuito integrado MAX7404.

Todos los bloques internos del microcontrolador seleccionado son configurados por la Unidad de Procesamiento Central (CPU por sus siglas en inglés). Se constituye por un núcleo compatible con 8051, una memoria de 256 bytes de SRAM, y una memoria de programa de 8kByte de FLASH. De acuerdo al esquema presentado en la figura 2, el bloque CPU ejecuta una secuencia de programa y especifica los parámetros y regímenes de trabajo del subsistema de transmisión. El esquema eléctrico de las conexiones del microcontrolador del subsistema de transmisión se ilustra en la figura 6.

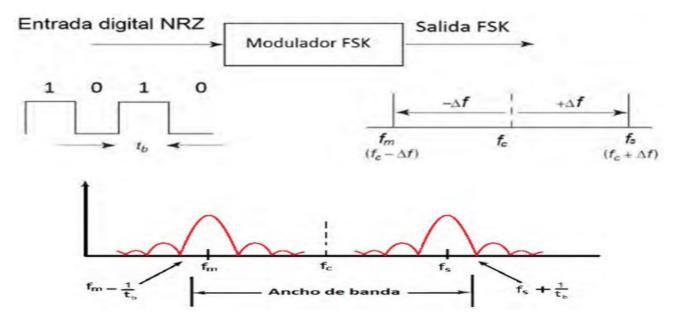

#### 3.3.- CIRCUITO MODULADOR BFSK

No es práctico propagar señales de información en banda base a través de los canales de comunicación como el cableado, la atmósfera, etc. Es necesario modular la fuente de información con una señal analógica de mayor frecuencia, llamada portadora. La modulación no es más que el proceso de cambiar una o más propiedades de la portadora en proporción con la señal de información. En el caso de la modulación digital es el proceso mediante el cual se incorpora la información que poseen determinados símbolos digitales en forma de onda compatibles con las características del canal; lo que se logra variando la fase, amplitud o frecuencia de una señal denominada portadora. Este proceso se lleva a cabo en el bloque transmisor, que es el encargado de acoplar la señal al canal de comunicaciones para combatir efectos indeseables, tales como la distorsión de amplitud, el ruido, la atenuación y la interferencia [13]. Este trabajo presenta el diseño de un circuito modulador BFSK no coherente usando el microcontrolador C8051F520 el cual se muestra en la figura 6.

Figura 6: Esquema eléctrico del circuito modulador con el microcontrolador C8051F520.

En el diseño se emplea el periférico embebido PCA del microcontrolador C8051F520, este se configura para generar las frecuencias de transmisión de 'F0' y 'F1', por los pines de puerto de P0.2 y P0.3 respectivamente. El pin de transmisión del puerto serie UART, dado en P0.4, se conecta a la entrada de selección del circuito integrado TSA3159 con el fin multiplexar dichas frecuencias en correspondencia al valor binario transmitido, obteniéndose a la salida una señal con modulación BFSK no coherente.

La modulación BFSK se caracteriza por ser de amplitud y potencia constante. Los efectos en la variación de amplitud que ocurren mayormente afectan poco la demodulación, dado que la información está presente en los cambios de frecuencia. También es aplicable en receptores pasivos (no amplifican la señal recibida) dado que con poco nivel de amplitud se garantiza la demodulación. Para la selección de las frecuencias 'F0' y 'F1' se tiene en cuenta la velocidad de transmisión del puerto serie y el contenido espectral que genera una señal BFSK como se ilustra en la figura 7.

Figura 7: Análisis espectral de una señal BFSK [9].

En el caso de la elección del código de línea se tiene en consideración que estos tienen como propósito transmitir información desde un emisor hacia un receptor a través de un enlace o canal. para este trabajo se selecciona el código denominado como NRZ (de las siglas del inglés de No Return to Zero [14]. Se utiliza como entrada digital del modulador BFSK la señal de transmisión del puerto serie asincrónico del microcontrolador C8051F520. Dado que se tiene una velocidad de transmisión 'fb' de 115200 baudios, esto corresponde a un tiempo de bit 'tb' de 8.6 us. Para una señal BFSK el ancho de banda mínimo debe ser dos veces mayor igual que la velocidad de transmisión ( $B \ge 230,4 \text{ kHz}$ ), por ende, se escoge así una frecuencia F0 ( $f_m$ ) y F1 ( $f_s$ ) de 1 MHz y 1.5 MHz respectivamente. De estos valores se obtiene la desviación máxima de frecuencia y el ancho de banda de transmisión, empleando las ecuaciones 1 y 2:

$$\Delta f = \frac{|\text{fm-fs}|}{2} = 250 \text{ kHz} \tag{1}$$

$$B = 2(\Delta f + fb) = 730.4 \, kHz \tag{2}$$

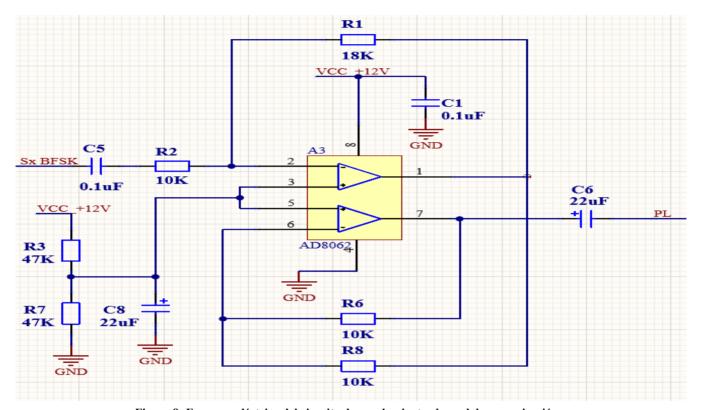

#### 3.4.- CIRCUITO DE ACOPLAMIENTO AL CANAL DEL S-TX

El circuito de acoplamiento al canal del S-TX tiene la función fundamental de amplificar la portadora de la señal de información con el objetivo de contrarrestar los niveles de atenuación a las altas frecuencias que presenta el canal de comunicación. Además, este circuito lleva a cabo las funciones fundamentales relacionadas con los filtros de acoplamiento, drenaje de corriente de carga y aislamiento de la línea de alimentación [15]. Por tanto, esto permite alcanzar la distancia máxima requerida para obtener la señal de información en el lado del subsistema de recepción. Por otro lado, debido a que el pin de salida del microcontrolador no entrega suficiente corriente, este circuito eleva la potencia necesaria a la portadora BFSK para su transmisión a través del par trenzado de cobre.

Para el diseño de este circuito se utiliza el circuito integrado AD8062, como se observa en la figura 8. Este posee dos amplificadores operacionales de potencia, los cuales se conectan en cascada en configuración inversor con una etapa inicial de ganancia de 1.8 veces y la otra de ganancia unitaria para que no exista distorsión de la señal. Además, se polarizan ambos operacionales con un divisor resistivo a la mitad de su voltaje de alimentación, y se emplea el capacitor de desacople C6 que con la impedancia de la red crea un filtro paso alto, de modo que elimina la componente de directa y acopla dicha señal en la red sobre la componente de directa de 12 V.

Figura 8: Esquema eléctrico del circuito de acoplamiento al canal de comunicación.

#### 4.- DISEÑO DEL SUBSISTEMA DE RECEPCIÓN

De igual modo que en el S-TX se tienen en consideración las funciones correspondientes al subsistema de recepción (S-RX) y los requisitos técnicos del sistema propuesto, para realizar la selección de los componentes requeridos y efectuar su diseño. Se mencionan a continuación los componentes que se emplean en este subsistema.

- Circuito integrado regulador de voltaje a 5V, LM7805.

- Microcontrolador de la familia SiLabs, C8051F520 (incorpora un núcleo compatible 8051 con otros periféricos analógicos y digitales).

- Circuito integrado de TEXAS INSTRUMENTS, 4046B (presenta un PLL (de las siglas del inglés de *Phase-Locked Loop*)).

- Circuito integrado de ON SEMICONDUCTOR, MC33178D (presenta dos amplificadores operacionales de bajo ruido)

- Circuito integrado de ANALOG DEVICES, AD8062 (incluye dos amplificadores operacionales de alta frecuencia)

- Circuito integrado del MAXIM, MAX7404 (incluye un filtro pasa-bajo de orden 8 con capacitores-conmutados)

- Componentes de misceláneas relacionados a resistores, transistores, capacitores e inductores.

## 4.1.- CIRCUITO DE ACOPLAMIENTO AL CANAL DEL S-RX

Al igual que en el subsistema de transmisión se emplea el mismo circuito de acoplamiento al canal en el subsistema de recepción basado en los amplificadores de operacionales AD8062. Este realiza la función de desacoplar la componente de directa del canal, y amplifica la señal portadora BFSK en el rango de entrada admisible al circuito demodulador, y su esquema eléctrico es similar al mostrado anteriormente en la figura 8.

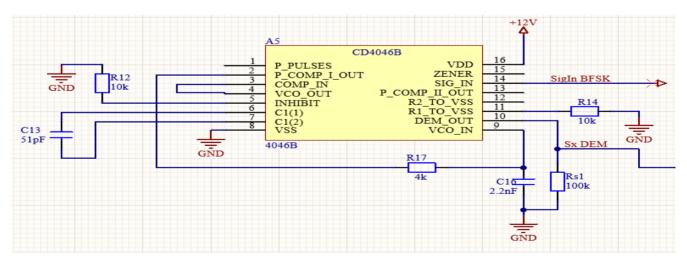

#### 4.2.- CIRCUITO DEMODULADOR BFSK

El circuito demodulador BFSK se encarga de extraer la señal de información de la portadora y trasladar su contenido espectral a banda base. Para su diseño se usa el circuito integrado CD4046B que incluye una red PLL con dos comparadores de fase, un oscilador controlado por voltaje (VCO, por sus siglas en inglés), y un seguidor de fuente, véase [16].

En la entrada de este circuito se aplica la señal portadora BFSK, la cual se compone de dos señales con frecuencia de 1MHz y 1.5MHz, usadas ambas para la transmisión del bit '0' y '1' respectivamente. Según las especificaciones de este integrado, para que su red PLL se enganche a estos valores de frecuencias, se le debe alimentar con un voltaje superior a los 10 V, se escoge en esta investigación un voltaje de alimentación de 12 V. Por tanto, la señal BFSK debe estar en el rango de 1 a 12 V para su demodulación efectiva.

Para el diseño de este circuito resulta necesario seleccionar los valores de los componentes R1 y C1, estos establecen la frecuencia central de enganche de la red PLL. Para esta investigación teniendo en cuenta que el voltaje de alimentación es de 12 V, se escoge los valores de  $R14 = 10 \text{ k}\Omega$  y C13 = 51 pF, esta configuración permite que el VCO oscile a una frecuencia de central de 1.2 MHz a la mitad del voltaje de alimentación en su entrada. Otro aspecto importante a considerar en el diseño es el filtro pasa bajo (dado por los valores de los componentes de R3 y C2) de seguimiento de fase, que comprende la señal de error aplicada a la entrada del VCO para corregir el desfasaje respecto a la portadora BFSK. Este filtro pasa bajo debe poseer una frecuencia de corte dos veces superior a la velocidad de transmisión configurada (que en este caso se refiere a 115.2 kHz), y atenuar los más posibles las frecuencias asociadas al bit '0' y bit '1' que presenta la portadora BFSK. Por ende, como se muestra en la figura 9, se seleccionó los valores de  $R17 = 4 \text{ k}\Omega$  y C16 = 2.2 nF y se establece una frecuencia de corte de 250 kHz. En este trabajo no se utilizó la resistencia R2 para darle mayor rango de enganche a la red PLL, y una resistencia en la salida de demodulación  $Rs = 100 \text{ k}\Omega$ .

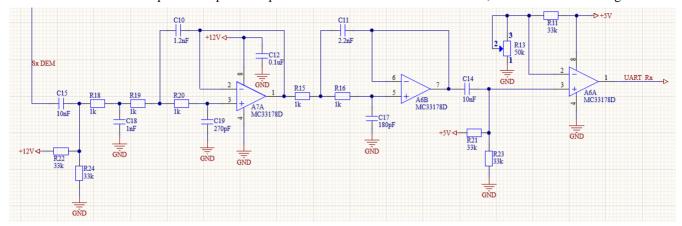

Figura 9: Esquema eléctrico del circuito PLL utilizado.

Debido a que la demodulación que genera el circuito presenta aún una porción de ruido se pasa a través de un filtro activo pasa-bajo de quinto orden con una frecuencia de corte en 230 kHz. Esta señal fluctúa su amplitud entre el nivel de voltaje asociado al bit '0' y al bit '1' sobre un nivel de directa igual a la mitad del voltaje de alimentación del circuito. La señal filtrada se conecta a una entrada de un comparador de voltaje y la otra presenta una referencia de voltaje establecida con

divisor resistivo. Este debe presentar el mismo voltaje de alimentación del bloque microcontrolador del S-RX, para acondicionar dicha señal al pin de recepción del puerto serie UART del microcontrolador, como se ilustra en la figura 10.

Figura 10: Esquema eléctrico del filtro de quinto orden seguido del comparador de voltaje.

## 4.3.- DISEÑO DEL BLOQUE MICROCONTROLADOR DEL S-RX

De igual forma, para el bloque microcontrolador del S-RX se emplean el integrado C8051F520, ya que dispone de los recursos necesarios que se proponen en el diseño del subsistema de recepción mostrados en la figura 1. Este se encarga fundamentalmente de la recepción y procesamiento de la señal digital de información en banda base a través del puerto de serie UART.

En este caso, se configura el puerto serie UART del microcontrolador C8051F520 por interrupción a una velocidad de recepción de 115200 baudios por segundos. Los datos se reciben y almacenan para su posterior análisis y procesamiento en un búfer de recepción de tipo FIFO (bloque RXFIFO), véase la figura 1. A partir de los datos obtenidos en el bloque RXFIFO, el procesador ejecuta una máquina de estado con el objetivo de decodificar la estructura de datos con la secuencia de preámbulo y el identificador de sincronismo, para lograr la sincronización en byte y en trama. En caso de no encontrar en el búfer dicha secuencia de datos se descarta la trama.

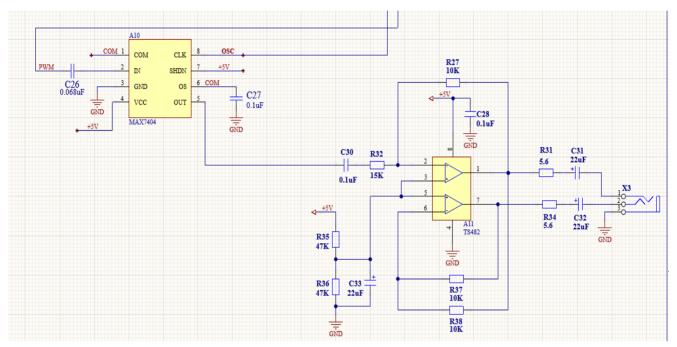

Si existe una trama de datos válidos, se procede a extraer las muestras de la señal y se envían al bloque DAC (que en este caso se refiere al periférico PCA configurado en el modo de modulación por ancho de pulso de 8-bit (PWM, por sus siglas en inglés). Para el proceso de envío de muestras se configura el temporizador TIMER2 (bloque TIMER2) del microcontrolador a la misma frecuencia de digitalización dada en el subsistema de transmisión de 8kHz. Cada muestra se transmite sobre una portadora PWM de una frecuencia mayor o igual a diez veces este valor. Además, se usa otro módulo del periférico PCA para generar el reloj que establece la frecuencia de corte a este filtro pasa-bajo. En la figura 11, se muestra en el esquema eléctrico asociado microcontrolador del subsistema de recepción con sus señales correspondientes.

Figura 11: Esquema eléctrico del microcontrolador del subsistema de recepción.

#### 4.4.- CIRCUITO DE RECUPERACION DE SEÑAL

El diseño del circuito de recuperación se constituye de un filtro pasa-bajo y una etapa de amplificación de señal usando el circuito integrado MAX7404 y TS482 respectivamente. El filtro pasa-bajo se utiliza para eliminar la portadora PWM y recuperar de esta forma la señal de información a su naturaleza analógica, su frecuencia de corte se establece en el valor de 3800 Hz a través del reloj que proporciona el microcontrolador. Se usa el integrado TS482 para amplificar y ajustar la señal de información. En la figura 12, se muestra el esquema eléctrico del circuito de recuperación de señal.

Figura 12: Esquema eléctrico del circuito de recuperación de señal.

#### 5.- RESULTADOS

Para el análisis de los resultados de la presente investigación se lleva a cabo la determinación de la calidad objetiva y subjetiva del enlace BFSK sobre el canal DC-PLC teniendo en consideración las recomendaciones establecidas por la UIT (Unión Internacional de Telecomunicaciones).

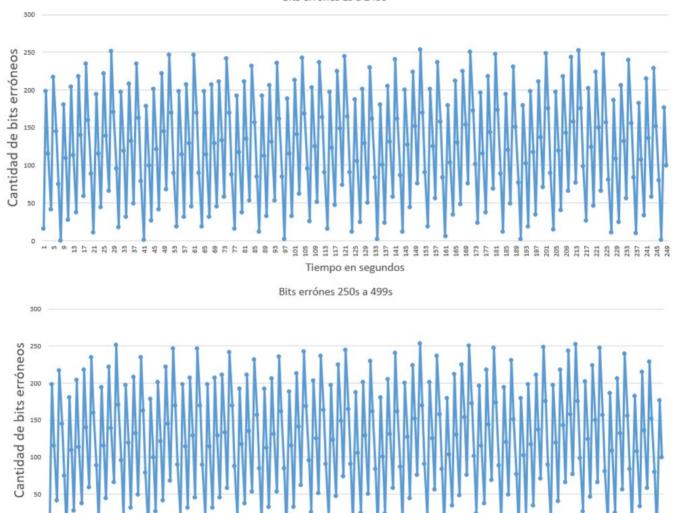

#### 5.1. DETERMINACIÓN DE LA CALIDAD OBJETIVA DEL ENLACE BFSK

Para la determinación de la calidad objetiva del enlace BFSK se realiza la medición de la razón de bits erróneos (BER, por sus siglas en inglés) que se establece sobre el canal DC-PLC. Se prepara la maqueta experimental para medir la cantidad de bit erróneos transmitidos durante un segundo, usando como canal de comunicación un cable par trenzado de longitud de 100m. Esta medición se repite cíclicamente hasta alcanzar una población de 1000 muestras de dicha variable. En el Anexo B se recogen en tablas los valores obtenidos de las cantidades de bits erróneos alcanzados cada 1 segundo. El cálculo del parámetro BER en porciento se lleva a cabo usando la siguiente ecuación:

$$\%BER = \frac{Bits\ err\'oneos}{Bits\ trasmitidos}\ x\ 100 = \frac{Bits\ err\'oneos}{12000\ x\ 10\ bit}\ x\ 100$$

(3)

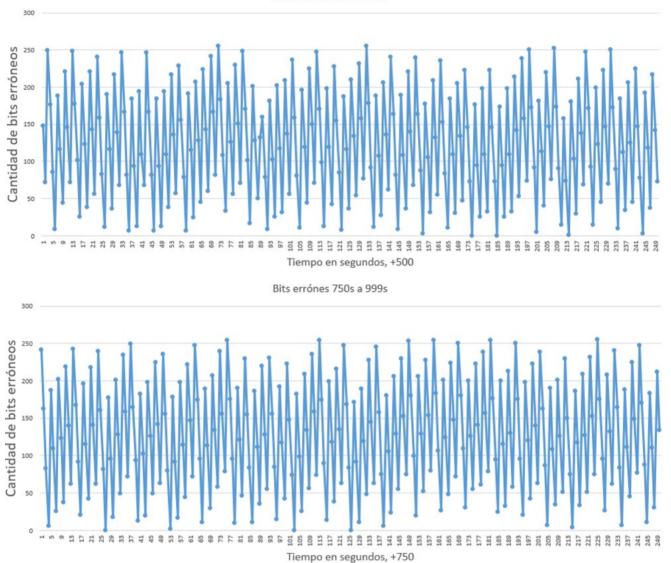

Los bits trasmitidos en un tiempo de 1 segundo equivalen a una cantidad de 120000 bit, este periodo se obtiene a partir de la transmisión cada 86 µs de 12000 bytes de datos, en el cual cada dato se representa en 10 bit (un bit Start, 8 bit de datos, un bit Stop). A partir del análisis de los valores obtenidos de cantidad de bits erróneos durante un intervalo de 1000 segundos,

como se ilustra en las figuras 13 y 14, se refleja el caso crítico con un valor máximo de 255 bit erróneos, por lo que esto resulta una tasa de BER de 0.2% mostrada en el cálculo de la ecuación 4. Este valor de BER se considera admisible para la transmisión digital de una señal de voz [17].

$$\%BER = \frac{255 \ bit \ err\'oneos}{120000 \ bit} \ x \ 100 = 0.2 \% \tag{4}$$

Bits errónes 1s a 249s

Figura 13: Medición de las cantidades bits erróneos cada 1s en el intervalo de 1 a 499s.

Bits errónes 250s a 499s

Figura 14: Medición de las cantidades bits erróneos cada 1s en el intervalo de 500 a 999s.

## 5.2.- DETERMINACIÓN DE LA CALIDAD SUBJETIVA DEL ENLACE BFSK

La determinación de la calidad subjetiva del enlace BFSK se lleva a cabo con la transmisión de la señal de voz sobre el canal DC-PLC a diferentes distancias entre el subsistema transmisión y recepción para su evaluación teniendo en cuenta el término referido como notas medias de opinión (MOS, de las siglas en inglés de Mean Opinion Score).

Las notas medias de opinión se definen con valores de una escala predefinida por un sujeto a su propia opinión sobre la calidad de funcionamiento del sistema de transmisión utilizado para una conversación o únicamente para una escucha de material hablado [18]. Considerando este término en una escala predefinida del parámetro MOS entre 1 y 5, se calificaron por cinco sujetos expertos los resultados mostrados en la tabla 3.1 durante 5 minutos para cada distancia. La calidad de la señal subjetiva se refiere al promedio de las evaluaciones proporcionadas por los expertos.

Tabla 3.1 Valoración subjetiva de la señal de voz a través del MOS.

| Parámetro                                                            | Distancia entre el STx y el SRx | Calidad de la<br>señal |

|----------------------------------------------------------------------|---------------------------------|------------------------|

| Valoración<br>Subjetiva<br>de la<br>calidad de<br>la señal de<br>voz | 10 m                            | 5                      |

|                                                                      | 20 m                            | 5                      |

|                                                                      | 30 m                            | 5                      |

|                                                                      | 40 m                            | 4                      |

|                                                                      | 50 m                            | 4                      |

|                                                                      | 60 m                            | 2                      |

|                                                                      | 70 m                            | 1                      |

|                                                                      |                                 |                        |

## **6.- CONCLUSIONES**

Con la realización de este trabajo se logró el diseño de un sistema de comunicación que permite la transmisión digital de señales de voz a través de canal de línea de potencia de corriente de directa usando la modulación BFSK. Se hizo uso de los microcontroladores con núcleo 8051 de la familia Silicon Laboratories, específicamente el integrado C8051F530, en la propuesta de diseño del sistema DC-PLC. Se asimiló y profundizó los principios de diseño de las tecnologías DC-PLC, se analizaron las variantes de soluciones de circuitos de acoplamiento que se utilizan.

También se consolidaron los criterios de necesarios para el diseño de un circuito modulador BFSK no coherente a partir de la conmutación y selección de dos señales de frecuencias para la transmisión del bit '0' y el bit '1' usando el microcontrolador C8051F530. Se obtuvo un demodulador BFSK usando el circuito integrado PLL (CD4046B) en conjunto con un filtro activo pasa-bajo de quinto orden a una frecuencia de corte de 230 kHz.

La solución de diseño obtenida para el subsistema de transmisión y el subsistema de recepción de información sobre la red DC-PLC es sencilla y de bajo costo implementación. Además, esta permite satisfacer los requerimientos exigidos para ambos subsistemas que deben ser de bajo consumo y de dimensiones pequeñas.

#### REFERENCIAS

- 1. Ndjiongue AR, Ferreira HC. Power line communications (PLC) technology: More than 20 years of intense research. Transactions on Emerging Telecommunications Technologies. 2019;30(7):3575-3594.

- 2. Sung GN, Wu CM, Huang CM. The sensor network using DC power line communication bus. En: 2015 IEEE Symposium on Computer Applications & Industrial Electronics (ISCAIE) [Internet]. Langkawi, Kedah, Malaysia: IEEE; 2015. p. 197-200. Disponible en: http://ieeexplore.ieee.org/document/7298355/.

- 3. Zaqout IS, Abu Nasr MH, Abu Naser BS. VoIP Using Power Line Communications. Journal of Al Azhar University-Gaza (Natural Sciences). 2017;19(1):57-81.

- 4. Liton AM, Qi ZJ, Jun LY. Review Article, Broadband Power Line Communication and Internet of Things in Smart Building Applications. International Journal of Research in Engineering and Science (IJRES). 2022;10(3):68-71.

- 5. Maryanka Y, Priel E. CAN, LIN, RS232/485 over DC powerline Challenges and semiconductor solutions. En: Embedded World Conference 2020 [Internet]. Nuremberg, Germany: Desing & Elektronik; 2020. p. 1-3. Disponible en: https://www.researchgate.net/publication/340665107.

- 6. Mlýnek P, Rusz M, Benešl L, Sláčik J, Musil P. Possibilities of Broadband Power Line Communications for Smart Home and Smart Building Applications. Sensors. 2021;21(1):240-256.

- 7. Debita G. BPL-PLC Voice Communication System for the Oil and Mining Industry. Energies. 2020;13(18):4763-4781.

- 8. Ajenikoko GA, Ojekunle EO. Investigative Study of Voice and Data Communication over Power Line Communication System. Mathematical Theory and Modeling. 2019;9(8):20-37.

- 9. Apaza-Mamani V, Zenteno-Bolaños E. High-Speed audio communications in domestic power line channels. En: 2017 IEEE XXIV International Conference on Electronics, Electrical Engineering and Computing (INTERCON) [Internet]. Cusco, Perú: IEEE; 2017. p. 27-30. Disponible en: https://ieeexplore.ieee.org/document/8079673.

- 10. Tonello M, Swart TG. Power Line Communications Principles, Standars and Applications from Multimedia to Smart Grid [Internet]. Second Edition. Vol. XXV. Chichester, West Sussex, United Kingdom: Wiley; 2016. 591 p. Disponible en: http://lccn.loc.gov/2015048934.

- 11. Samakande T, Shongwe T, de Beer AS, Ferreira HC. The effect of coupling circuits on impulsive noise in power line communication. En: 2018 IEEE International Symposium on Power Line Communications and its Applications (ISPLC) [Internet]. Manchester, United Kingdom: IEEE; 2018. p. 1-5. Disponible en: https://ieeexplore.ieee.org/document/8360232/.

- 12. Datasheet C8051F52x/F52xA/F53x/F53xA, 8/4/2 kB ISP Flash MCU Family. Silicon Laboratories; 2009.

- 13. Toledo K, Torres J. Demodulación de señales digitales mediante microcontroladores PIC18F4550. Revista Cubana de Ingeniería. 2013; IV (3):61-66.

- 14. Stallings W. Comunicaciones y Redes de Computadores. 6ta Edición. España: Prentice Hall; 1999. 741 p.

- 15. Ogunlade MA, Gbadamosi SL, Owolabi IE, Nwulu NI. Noise Measurement, Characterization, and Modeling for Broadband Indoor Power Communication System: A Comprehensive Survey. Energies. 2023;16(3):1535-1560.

- 16. Datasheet CMOS Micropower Phase-Locked Loop CD4046B. Texas Instruments; 2003.

- 17. ITU-T Rec. G.826 (12/2002) End-to-end error performance parameters and objectives for international, constant bit-rate digital paths and connections. [Internet]. Telecommunication Standardization Sector of ITU; 2002. Disponible en: https://www.itu.int.

- 18. Rec. UIT-T P.800.2 (2016) Interpretación y notificación de las notas medias de opinión [Internet]. Sector de Normalización de las Telecomunicaciones de la UIT; 2016. Disponible en: https://www.itu.int.

#### **CONFLICTO DE INTERESES**

Ninguno de los autores manifestó la existencia de posibles conflictos de intereses que debieran ser declarados en relación con este artículo.

#### CONTRIBUCIONES DE LOS AUTORES

**Wagner Gómez Gómez:** Conceptualización, Curación de datos, Análisis formal, Investigación, Metodología, Administración de proyecto, Redacción borrador original, Redacción-revisión y edición final.

Yosbel J. Herrera Fonseca: Recursos, Conceptualización, Metodología, Software, Supervisión, Redacción-revisión y edición.

Ismael Lavandera Rodríguez: Redacción-revisión y edición.

Enrique Ernesto Valdés Zaldívar: Supervisión, Redacción-revisión y edición.

#### **AUTORES**

**Wagner Gómez,** Ingeniero Automático, Centro de Investigaciones y Desarrollo Tecnológico, La Habana, Cuba. Email wgomez1389@gmail.com. Desarrollo de sistemas de transmisión de señales usando PLC. ORCID: 0000-0002-2115-8240

**Yosbel J. Herrera Fonseca**, Ingeniero en Telecomunicaciones y Electrónica, Master en Ciencias, Centro de Investigaciones y Desarrollo Tecnológico, La Habana, Cuba. Email <u>yj85herrera@gmail.com</u>. Procesamiento Digital de Señales en la especialidad de Radiofrecuencias. ORCID: 0000-0003-0586-1558.

**Ismael Lavandera Rodríguez**, Ingeniero Radio Eléctrico, Doctor en Ciencias, Centro de Investigaciones y Desarrollo Tecnológico, La Habana, Cuba. Email Ismael@tele.cujae.edu.cu. Dispositivos Activos y pasivos de microondas. ORCID: 0000-0001-5660-4928.

**Enrique Ernesto Valdés Zaldívar,** Ingeniero en Telecomunicaciones y Electrónica, Doctor en Ciencias, Centro de Investigaciones de la Microelectrónica, La Habana, Cuba. Email <u>enrique.valdes@cime.cujae.edu.cu</u>. Instrumentación Electrónica Avanzada con la utilización de la herramienta de LabVIEW. ORCID: 0000-0002-9430-2370.

Esta revista se publica bajo una Licencia Creative Commons Atribución-No Comercial-Sin Derivar 4.0 Internacional