# Procesadores modernos con sólo unos Clicks

Modern processors with just a few clicks

Lilian Bossuet<sup>†1</sup> and Carlos Andres Lara-Nino\*2

<sup>†</sup>Université Jean Monnet Saint-étienne, CNRS, Laboratoire Hubert Curien UMR 5516, F-42023 SAINT-ETIENNE 42000, France

$^1 \verb|lilian.bossuet@univ-st-etienne.fr|$

\*Universitat Rovira i Virgili, Departament d'Enginyeria, Informàtica i Mathemàtiques TARRAGONA 43003, Espanya

> <sup>2</sup>carlos.lara@fundacio.urv.cat Recibido: 16/04/24; Aceptado: 17/05/24

Resumen-Algunos programas educativos en áreas de ingeniería y tecnologías a menudo tienen dificultades para proveer a sus estudiantes con los instrumentos necesarios para realizar trabajos experimentales. Esto puede deberse a dificultades económicas o simplemente por falta de oportunidades para adquirir suficientes dispositivos. En estos casos, el diseño asistido por computadora podría adoptarse para modelar un gran número de dispositivos con bajos costos de operación. En este artículo se describe el uso del simulador gem5 como una herramienta que puede ser de utilidad para estudiantes de educación superior en las áreas de ingeniería e informática. Revisaremos el reto que representa para los estudiantes el tener acceso a placas de prototipado modernas y describiremos cómo el uso de un simulador puede resolver este problema hasta cierto punto. Finalmente, ilustraremos paso a paso el uso del simulador gem5 para emular un microprocesador moderno.

Palabras clave: ARM; RISC-V; gem5; emulación de microprocesadores.

Abstract— Some educational programs in areas of engineering and technology often have difficulties providing their students with the necessary instruments to carry out experimental work. This may be due to financial difficulties or simply a lack of opportunities to purchase enough devices. In these cases, computer-aided design could be adopted to model a large number of devices with low operating costs. This article describes the use of the gem5 simulator as a tool that can be useful for higher education students in the areas of engineering and computer sciences. We will review the challenge for students of having access to modern prototyping boards and describe how the use of a simulator can solve this problem to some extent. Finally, we will illustrate step by step the use of the gem5 simulator to emulate a modern microprocessor.

$\label{lem:eq:condition} \textbf{Keywords: ARM; RISC-V; gem5; microprocessor emulation.}$

#### I. Introducción

El desarrollo de la educación en las áreas de ingeniería y computación va de la mano con el uso de plataformas de prototipado que permiten al alumno efectuar actividades prácticas y conducir experimentos para enriquecer su formación profesional [1], [2]. Desafortunadamente, muchos estudiantes carecen de acceso a estos dispositivos. Dada la realidad socioeconómica de Latinoamérica [3], no es una expectativa razonable pensar que todos los alumnos podrían adquirir una tarjeta de pruebas sólo porque una asignatura la requiere. Si la institución educativa tiene la posibilidad de prestar estas tecnologías a sus estudiantes, este servicio

generalmente viene con restricciones horarias y está sujeto a la disponibilidad del material. Sin mencionar que, para un programa académico promedio, resultará complicado adquirir distintas versiones de la misma tecnología. Por ejemplo, se tendrá acceso a tarjetas Arduino con un procesador AVR<sup>®</sup>. Sistemas que son generalmente reservados para tareas básicas de prototipado [4], [5].

Aunado a esto, quienes hayan tenido la experiencia de gestionar la adquisición de sistemas de procesamiento modernos en cantidades moderadas (unos 12 dispositivos) estarán al tanto del impacto de la escasez global de semiconductores [6], [7]. Hay largas listas de espera con tiempos de entrega que van de meses a años. Para un centro de formación esto se traduciría en al menos una promoción que no tendrá acceso a la tecnología recientemente adquirida. Para un alumno esto resultará en tener que buscar los dispositivos en mercados alternos, usualmente con sobreprecios.

Sin duda, habrá un grupo significativo de centros de educación superior con ofertas formativas en ingenierías y computación en los que los alumnos no puedan acceder a plataformas de pruebas para desarrollar las actividades prácticas deseables. Desafortunadamente, un alto número de estudiantes llegará a optar por estas alternativas de formación, ya sea por limitantes económicos o por la proximidad a sus lugares de origen.

En todos estos casos, es imperativo identificar alternativas que permitan un acceso a la tecnología con bajo costo y alta disponibilidad [8], [9]. Que sean flexibles y puedan adaptarse a los avances en la investigación y desarrollo para brindar a los usuarios la oportunidad de generar experiencia con tecnologías de punta. Esto sin duda se verá reflejado en mejores oportunidades laborales y un mercado más laboral más competitivo.

En este artículo, proponemos hacer uso de *gem5*, un emulador de arquitecturas hardware preciso a nivel de ciclos (*cycle accurate*) para enriquecer los procesos de formación que involucren el estudio de sistemas de cómputo embebido. Estos dispositivos, llamados procesadores modernos, incluyen arquitecturas como ARM y RISC-V, tecnologías muy utilizadas en la industria y la investigación avanzada. Mediante el uso de la emulación de estos sistemas, buscamos solventar problemas relacionados con la adquisición y acceso a las tecnologías. No obstante, existen retos asociados con la adopción de *gem5*. Uno de los principales su complejidad

5

inicial de uso. Por eso parte de este documento detalla paso a paso el proceso para utilizar esta herramienta.

El resto del documento se estructura de la siguiente manera. En la Sección II proporcionamos nociones básicas de virtualización para permitir al lector comprender a grandes rasgos la estrategia propuesta. Después, en la Sección III hablamos sobre distintos sistemas existentes que permiten la emulación de circuitos digitales. En la Sección IV se introduce *gem5* y se detallan sus particularidades mientras que la Sección V proporciona distintos ejemplos para su uso. Finalmente, la Sección VI cierra el artículo con nuestras conclusiones y comentarios finales.

#### II. UNA COMPUTADORA DENTRO DE OTRA

En mayor o menor medida, se puede constatar que el acceso en Latinoamérica a equipos de cómputo se ha incrementado a lo largo de los años. Estos sistemas de cómputo distan mucho de los microcontroladores requeridos en la formación de ingenierías y computación. Primero, su tamaño y especificaciones difieren: la cantidad de memoria disponible será superior en una computadora, está tendrá uno o varios procesadores más potentes, y el sistema de alimentación es generalmente constante. Podríamos llegar a la conclusión que una computadora (procesador) será generalmente superior a una tarjeta de prototipado (microprocesador). Pero al mismo tiempo, no es sencillo programar los procesadores de una computadora como lo haríamos con una tarjeta Arduino, o tener el mismo grado de acceso a sus periféricos. ¿Cómo hacer entonces para utilizar los equipos de cómputo con mayor disponibilidad para emular el comportamiento de un microprocesador que es difícil de conseguir?

Figura 1: Si consideramos que una computadora es un procesador grande, es lógico pensar que sería posible modelar un procesador más pequeño dentro de este sistema. El procesador más pequeño puede entonces contener sus propias aplicaciones o programas.

En las ciencias de la computación existe la noción de *máquina virtual*, que se aplica para el caso donde utilizamos un programa de computadora que va a emular otra computadora dentro del equipo. Claramente, como se ilustra en la Fig. 1, la computadora interna será más limitada que la máquina física. No obstante, esta estrategia puede ser de utilidad para tener acceso a un sistema operativo distinto sin

necesidad de modificar el equipo, o para probar la ejecución de algunas aplicaciones en un entorno controlado.

Una de las herramientas más ampliamente utilizada para virtualizar microprocesadores es *qemu* [10], que toma su nombre del inglés "quick **emu**lator." Este programa de computadora permite emular el procesador de un sistema mediante la *traducción binaria dinámica* y proporciona múltiples modelos de hardware que permiten ejecutar una variedad de sistemas operativos o también aplicaciones en *bare metal* (sin sistema operativo).

Sin embargo, un entorno virtual permite simplemente replicar el comportamiento *lógico* del sistema que deseamos emular. En el mejor de los casos, trasladará todas las instrucciones del entorno virtual en código máquina que puede interpretar el hardware. En contraste, si se desea estudiar la cantidad de accesos a memoria, los fallos en la cache, o incluso la disipación de potencia de una plataforma, será necesario buscar otras alternativas.

#### III. EMULACIÓN DE HARDWARE

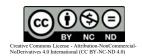

Al igual que hay emuladores del comportamiento lógico de una computadora, existe software dedicado a modelar la respuesta de un circuito electrónico, sea este analógico o digital. El más popular es sin duda SPICE [11] (del inglés "Simulation Program with Integrated Circuit Emphasis"). Esta herramienta permite, entre otras cosas, verificar que la operación de un circuito analógicos sea correcta y predecir su funcionamiento, como se muestra en la Fig. 2a. Desde su introducción en 1989, el éxito de este simulador se debe en gran medida a que es Open Source, esto quiere decir que el código fuente está disponible para todos, además que su uso es gratuito para actividades no lucrativas. Su desventaja principal es la complejidad de uso, ya que es necesario contar con los modelos matemáticos precisos de todos los componentes del sistema a analizar. Esto hace que el estudio de sistemas complejos, como un procesador moderno, sea prácticamente imposible.

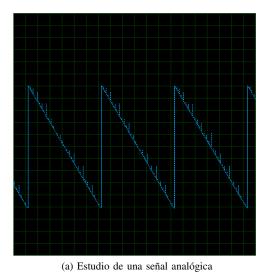

A pesar de la complejidad de los sistemas digitales, se tiene la ventaja de que su comportamiento está definido por ciclos de reloj. Esto se ilustra en la Fig. 2b. Evidentemente, para modelar fenómenos térmicos o eléctricos se necesitará una resolución menor, pero en general se considera que un modelo *cycle accurate* (preciso a nivel de ciclos) es aceptable. Para estas tareas se tienen herramientas como KTechLab que son de código abierto y gratuitas y que permiten analizar circuitos digitales complejos.

En la industria, encontramos soluciones más potentes como *Proteus Design Suite*<sup>®</sup>, que permiten estudiar el funcionamiento de componentes analógicos y digitales, así como microprocesadores con códigos internos modificables. La principal limitación para su uso en educación es su costo elevado. Es posible solicitar una licencia temporal para estudiantes, pero esta no permite guardar el estado del proyecto. Otra limitación de esta herramienta es que los modelos de los componentes son limitados y crear u obtener nuevos modelos resulta difícil si hemos de respetar la licencia de uso. Además, ¿qué pasa cuando es de interés estudiar rutinas de procesamiento más complicadas como un sistema operativo completo?

Figura 2: Para analizar una magnitud como el voltaje o la temperatura del circuito es necesario usar un periodo de simulación acorde a la variación de la señal. Por el contrario, para estudiar el comportamiento de un circuito digital es posible efectuar un análisis a la frecuencia del procesador.

## IV. UN SIMULADOR PARA HARDWARE Y SOFTWARE

Las limitaciones mencionadas en las previas secciones no aplican únicamente al caso de los estudiantes, sino que son problemas frecuentes alrededor del mundo. Así que algunos investigadores han respondido a las preguntas planteadas creando un sistema de simulación completo, gratuito y de código abierto, que permite la emulación de sistemas lógicos complejos, pero también modela el hardware subyacente.

Al combinar una iniciativa de la Universidad de Wisconsin llamada GEMS [12], que viene de "General Execution-driven Multiprocessor Simulator," con un proyecto de la Universidad de Michigan llamado M5 [13] (ambas instituciones de los EE. UU.) fue posible crear un simulador ahora conocido como *gem5* [14]. El logotipo del proyecto se muestra en la Fig. 3.

Figura 3: El simulador gem5 es gratuito y de código abierto.

Este sistema ofrece soporte nativo para la simulación de procesadores con arquitecturas del conjunto de instrucciones de tipo Alpha, ARM, SPARC, MIPS, POWER, RISC-V y x86. Es posible lanzar una simulación reducida del sistema conocida como *system-call emulation* (SE) o una simulación completa conocida como *full system simulation* (FS) que permite interactuar con el procesador y obtener estadísticas adicionales (disponible para Alpha, ARM, SPARC, RISC-V y x86). En particular, los modelos para ARM y RISC-V

proporcionan herramientas interesantes para el estudio de los microcontroladores utilizados en aplicaciones de vanguardia.

Existen ciertas limitantes principales para el uso de *gem5* en las tareas de educación. Primero, el software existe solo para sistemas operativos basados en Linux. Según datos recopilados por *statcounter* [15], para abril de 2022 casi el 75 % de las conexiones a internet provenientes de computadoras de escritorio y portátiles usaba Windows, mientras que apenas un 2.5 % usaba sistemas operativos basados en Linux. No se tienen estadísticas sólo para América latina, pero se puede esperar que el porcentaje de computadoras que usan Linux será menor. Mientras que es posible emular Ubuntu o Debian en una máquina virtual, esto no es recomendado para lanzar una simulación de *gem5*.

Lo que nos lleva a la segunda limitante: la complejidad de procesamiento. El tiempo requerido para completar una simulación tipo FS dependerá en gran medida de la arquitectura a emular y la carga de procesamiento. Por ejemplo, para una computadora portátil con un procesador i7 y 32 GB de RAM, emular Ubuntu en un procesador Cortex A-57 tomará algunos minutos; note que estas especificaciones estarán muy por encima de los sistemas de cómputo normalmente disponibles para un estudiante. Para solventar esta limitante, gem5 permite hacer uso de checkpoints y regions of interest que son instantáneas tomadas de la simulación que hacen necesario tener que ejecutar las tareas más pesadas sólo una vez y retomar el procesamiento en el punto de interés. Por ejemplo, si deseamos modificar sólo el archivo binario que será ejecutado en el microprocesador no sería práctico simular nuevamente todo el proceso de arranque del sistema.

La tercera característica que podríamos considerar como una limitante es la inclinada pendiente en la curva de aprendizaje para trabajar con *gem5*. El principal lenguaje del simulador es Python, lo que facilita su uso en cierta medida. No obstante, un usuario avanzado requerirá conocimientos puntuales de sistemas basados en Linux, programación en C/C++, uso de compiladores cruzados, arquitectura de computadoras, sistemas de memoria, e incluso sistemas de

control de versiones (*git*). Sin embargo, todo depende del cristal con que se mire. Estos conocimientos se necesitan para crear un modelo de simulación que una vez definido puede utilizar muchos usuarios. A su vez, trabajar en el diseño de estos modelos aportaría una amplia gama de conocimientos para los estudiantes.

# V. UN EJEMPLO DE USO

Para esta Sección supondremos que el equipo de trabajo cuenta con todas las dependencias necesarias [16]. También supondremos que el usuario cuenta con permisos de administrador para ejecutar algunas tareas. El ejemplo se ha creado en una computadora portátil con Ubuntu 20.04 y la versión v22.0.0.2 de *gem5* (Commit 1d03f6de941520860c673b5f7954c82a46e8b191).

Se propone la simulación completa de un chip ARMv8-A, que ha sido utilizado en una amplia gama de sistemas desde smartphones (Huawei Mate 9) hasta tarjetas de prototipado (Hikey 960). Uno de estos sistemas se muestra en la Fig. 4. Dentro del chip existe un *cluster* con varios núcleos Cortex-A57/A73 y un *cluster* con varios núcleos Cortex-A53 siguiendo una arquitectura big.LITTLE. El principal atractivo de este tipo de sistemas es su eficiencia energética al cambiar la carga de procesamiento de un clúster a otro según la demanda. En este microprocesador vamos a cargar el sistema operativo Ubuntu 18.04 y desde allí ejecutar una aplicación en C.

Figura 4: Un chip de la familia ARMv8-A. Las tarjetas de prototipado equipadas con estos microprocesadores tienen un costo en el mercado que ronda los 250 USD.

El primer paso por realizar es obtener una copia del código del simulador, algo que es tan sencillo como abrir una terminal y ejecutar el comando:

```

git clone https://gem5.googlesource.com/public/gem5

cd gem5

git checkout 1d03f6de941520860c673b5f7954c82a46e8b191

```

Cuando se acaba la descarga, se debe entrar al directorio creado y compilar el simulador. Esto se puede llevar a cabo con las instrucciones:

```

scons build/ARM/gem5.opt -j $(nproc)

```

Note que en este caso vamos a compilar el simulador para trabajar con arquitecturas ARM. Si se desea usar una ISA diferente se deberá modificar la segunda instrucción, por ejemplo scons build/X86/gem5.opt creará los componentes necesarios para simular sistemas X86. Adicionalmente, usaremos la extensión *opt*, pero igualmente se

podría lanzar gem5.debug o gem5.fast según el tipo de optimización deseado.

El proceso para compilar el simulador es largo y pesado. Por suerte solo es necesario efectuar una vez esta tarea. Cuando este ha terminado, procederemos a obtener algunos archivos binarios para conducir la simulación. Estos se pueden descargar usando:

```

mkdir common; cd common

wget http://dist.gem5.org/dist/v22-0/arm/aarch-system

-20220707.tar.bz2

tar -xf aarch-system-20220707.tar.bz2

wget http://dist.gem5.org/dist/v22-0/arm/disks/ubuntu

-18.04-arm64-docker.img.bz2

bzip2 -d ubuntu-18.04-arm64-docker.img.bz2

cd -

```

Dentro del directorio gem5/common/ ahora encontraremos binarios para el proceso de *boot*, imágenes del kernel de Linux, y discos con sistemas de archivos para el sistema operativo. En particular haremos uso de los archivos gem5/common/binaries/boot.arm64, gem5/common/binaries/vmlinux.arm64, y gem5/common/ubuntu-18.04-arm64-docker.img. Note que todos corresponden a la arquitectura AArch64 que se encuentra en los procesadores Cortex A53/A57.

En este punto ya se puede lanzar una simulación básica del sistema para verificar que todo se ha compilado correctamente. Para ello se hará uso de un *script* de simulación escrito en lenguaje Python. Dentro del directorio gem5/configs/example/arm se puede encontrar el archivo fs\_bigLITTLE.py que permite simular una arquitectura big.LITTLE genérica. En la terminal, dentro del directorio gem5/ se puede lanzar la simulación usando el comando:

```

./build/ARM/gem5.opt \

./configs/example/arm/fs_bigLITTLE.py \

--caches \

--bootloader=./common/binaries/boot.arm64 \

--kernel=./common/binaries/vmlinux.arm64 \

--disk=./common/ubuntu-18.04-arm64-docker.img

```

Para interactuar con el microprocesador simulado, en otra ventana de la terminal será necesario compilar la terminal virtual de *gem5* y conectarse con el simulador. Para ello basta utilizar los siguientes comandos:

```

cd gem5/util/term

make

./m5term 3456

```

Note que el puerto utilizado es el mismo indicado en la primera terminal donde se lanzó la simulación, generalmente aparecerá como:

```

system.terminal: Listening for connections on port 3456

```

Si todo ha marchado bien, la segunda terminal deberá indicar la bienvenida a Ubuntu y el *login* automático de la sesión de administrador. Una vez dentro de la simulación, esta puede finalizarse usando el comando:

```

m5 exit

```

Este es un caso muy básico donde se usan esencialmente todos los parámetros de una simulación genérica de la arquitectura. En las secciones siguientes vamos a crear el modelo de simulación para el ejemplo propuesto, para ello se creará un nuevo *script* de simulación para aplicar los cambios necesarios:

```

cd configs/example/arm/

cp fs_bigLITTLE.py Hikey960.py

gedit Hikey960.py &

cd -

```

#### V-A. Ajuste dinámico de frecuencias y voltajes

Una característica muy importante de los microprocesadores modernos es su capacidad para modificar su frecuencia y voltaje de operación en función de la demanda de procesamiento. Esta estrategia es conocida como DVFS, del inglés "Dynamic Voltage and Frequency Scaling."

El primer paso será agregar opciones al *script* para para poder *pasar* los parámetros al simulador desde la línea de comandos. En la función addOptions() se van a agregar tres argumentos y se editarán dos que ya existen:

En seguida se editará el modelo de los clústeres para enlazar los valores de voltaje proporcionados a cada procesador:

También será necesario activar el módulo para DVFS del simulador e indicar que use los dominios de reloj asignados a cada clúster:

Luego será necesario editar el archivo gem5/configs/example/arm/devices.py para asignar un ID válido a cada dominio de reloj. Note que este archivo también especifica los valores para las memorias cache utilizadas en la arquitectura a simular, por ende, para obtener un modelo más preciso del sistema sería necesario ajustar estos valores.

```

{\tt domain\_id=system.numCpuClusters())} \\ [\dots]

```

La arquitectura de una computadora está declarada en archivos de extensión dtb (devicetree blob) que son generados a partir de un archivo dts (devicetree source). Esta especificación es usada por el kernel para instalar los drivers necesarios que permitirán al sistema operativo controlar el dispositivo. gem5 cuenta con una herramienta que permite generar automáticamente un archivo dtb para cada simulación. No obstante, esta utilidad no permite enlazar correctamente los dominios de reloj para múltiples clústeres. De no usar un archivo dtb adaptado para el modelo, el segundo clúster no sería conectado correctamente al controlador de DVFS.

Afortunadamente, el código fuente del simulador también incluye algunas plantillas para generar archivos *dtb* par algunas arquitecturas familiares. Aun así, será necesario editar estas fuentes para obtener la especificación definitiva de la arquitectura a simular. En el ejemplo propuesto buscamos un sistema big.LITTLE con cuatro núcleos en ambos clústeres mientras que las plantillas genéricas sólo ofrecen hasta dos núcleos en el clúster principal.

Primero es necesario editar el archivo gem5/system/arm/dt/Makefile para agregar un nuevo objeto a la lista de compilación:

```

TARGETS=\

[...]

armv8_gem5_v1_big_little_4_4.dtb \

[...]

```

Después se debe editar el archivo gem5/system/arm/dt/armv8\_big\_little.dts para habilitar el controlador de energía de *gem5* e incluir la configuración big.LITTLE deseada:

```

[...]

#define _4_4 3

[...]

gem5_energy_ctrl@10000000 {

reg = <0x00 0x10000000 0x00 0x1000>;

compatible = "arm, gem5-energy-ctrl";

[...]

#elif CONF_CPUS == _4_4

CPU(0,0x0)

CPU(1,0x1)

CPU(2,0x2)

CPU(3,0x3)

CPU(4,0x104)

CPU (5, 0x105)

CPU(6,0x106)

CPU(7,0x107)

cpu-map {

cluster0 {

core0 { cpu = <&CPU0>; };

core1 { cpu = <&CPU1>; };

cpu = <&CPU2>;

core3 { cpu = <&CPU3>; };

cluster1 {

core0 { cpu = <&CPU4>; };

core1 { cpu = <&CPU5>; };

core2 { cpu = <&CPU6>; };

core3 { cpu = <&CPU7>; };

};

};

```

Finalmente, usar el comando make dentro del directorio gem5/system/arm/dt/ producirá el archivo armv8\_-gem5\_v1\_big\_little\_4\_4.dtb que será utilizado en la simulación.

Para probar que se ha habilitado el mecanismo de DVFS de manera correcta, ahora se puede lanzar una simulación más completa del sistema:

```

./build/ARM/gem5.opt \

./configs/example/arm/Hikey960.py \

--big-cpus 4 \

--little-cpus 4 \

--caches \

--bootloader=./common/binaries/boot.arm64 \

--kernel=./common/binaries/vmlinux.arm64 \

--disk=./common/ubuntu-18.04-arm64-docker.img \

--dtb=./system/arm/dt/armv8_gem5_v1_big_little_4_4.dtb \

--dvfs \

--big-cpu-clock 2362MHz 2112MHz 1805MHz 1421MHz 903MHz \

--little-cpu-clock 1402MHz 999MHz 533MHz \

--big-cpu-voltage 1.0V 0.99V 0.98V 0.97V 0.96V \

--little-cpu-voltage 0.87V 0.86V 0.85V

```

Para usar DVFS en *gem5* es necesario que el número de valores de frecuencia para un clúster sea el mismo que el número de valores de voltaje, y que ambos estén ordenados de manera decreciente. Note que es posible especificar los diferentes puntos de operación en voltaje y frecuencia del procesador sin necesidad de modificar el modelo, esto es gracias al uso de argumentos en el *script* de simulación.

#### V-B. Modelando el consumo de energía del sistema

Por defecto, gem5 genera algunas estadísticas de la simulación en el archivo gem5/m5out/stats.txt. Es posible usar este sistema para evaluar distintas métricas del procesador, por ejemplo, la cantidad de accesos o fallos en alguna de las memorias cache. Se puede también crear un modelo del consumo de energía. Para ello es necesario editar el script de la simulación. Primero será necesario definir un modelo de potencia para cada componente de interés. En este ejemplo revisaremos cómo proceder en el caso de los CPU, pero es posible también agregar modelos para las memorias u otros componentes.

En *gem5* un modelo de potencia extiende la clase PowerModel e implementa cuatro clases que a su vez extienden la clase MathExprPowerModel correspondientes con los estados de *ON*, *CLK\_GATED*, *SRAM\_RETENTION* y *OFF*. Cada modelo debe tener estos cuatro comportamientos, aunque es posible indicar que todos usen el mismo modelo:

```

[...]

class CpuPowerOn (MathExprPowerModel):

def __init__(self, cpu_path, **kwargs):

super(CpuPowerOn, self).__init__(**kwargs)

self.dyn = "voltage * 2 * {}.ipc".format(

cpu_path)

self.st = "4 * temp"

class CpuPowerOff(MathExprPowerModel):

dyn =

st = "0"

class CpuPowerModel(PowerModel):

__init__(self, cpu_path, **kwargs):

super(CpuPowerModel, self).__init__(**kwargs)

self.pm = [

CpuPowerOn(cpu_path),

CpuPowerOff(),

CpuPowerOff(),

CpuPowerOff(),

[...]

```

Aquí también es conveniente usar argumentos de la línea de comandos para controlar la adquisición de estas estadísticas, se agregará un argumento que permita habilitar la captura y otro que determine la tasa de adquisición:

```

def addOptions(parser):

[...]

parser.add_argument("--power-models", action="

store_true")

parser.add_argument("--stat-freq", type=float,

default=1.0E-3)

return parser

```

Finalmente, para agregar los modelos a la simulación e indicar la tasa de adquisición a utilizar es necesario editar el método principal del *script* de simulación:

Note que para estimar modelos del consumo de potencia es necesario usar un tipo de CPU llamado *timing*. En *gem5* existen CPUs de tipo *timing* o *atomic*, que a su vez pueden usarse para construir otros modelos. En esencia, los CPU de tipo *atomic* usan accesos atómicos a memoria mientas que los CPU de tipo *timing*, como su nombre lo indica, tienen un comportamiento que emula periodos de espera y latencias. Es decir, se aproximan mejor a un comportamiento real. Por defecto, el *script* base utilizado toma CPUs de tipo *timing*, pero esto también se puede cambiar usando argumentos en la línea de comandos, por ejemplo, se puede usar CPUs equivalentes a los de un chip Exynos:

```

./build/ARM/gem5.opt

./configs/example/arm/Hikey960.py \

--big-cpus 4 \

--little-cpus 4 \

--cpu-type=exynos \

--caches \

--dtb=./svstem/arm/dt/armv8 gem5 v1 big little 4 4.dtb \

--bootloader=./common/binaries/boot.arm64 \

--kernel=./common/binaries/vmlinux.arm64 \

--disk=./common/ubuntu-18.04-arm64-docker.img \

--big-cpu-clock 2362MHz 2112MHz 1805MHz 1421MHz 903MHz \

--little-cpu-clock 1402MHz 999MHz 533MHz \

--big-cpu-voltage 1.0V 0.99V 0.98V 0.97V 0.96V \

--little-cpu-voltage 0.87V 0.86V 0.85V \

-power-models '

--stat-freq 1.0E-3

```

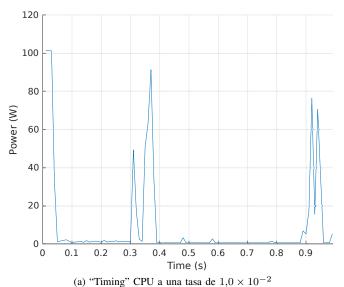

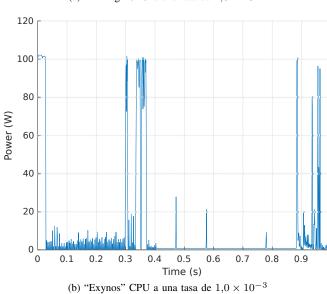

Cuando se analiza el contenido del archivo de estadísticas se puede identificar las relacionadas con los modelos de potencia. Para este ejemplo se tendrá la potencia estática y dinámica para cada uno de los ocho núcleos. La frecuencia de volcado está dada por el argumento --stat-freq. Al especificar una tasa de  $1.0\times10^{-2}$  esto equivale a calcular los modelos 100 veces por segundo simulado, mientras que una tasa de  $1.0\times10^{-3}$  será equivalente a calcular estos datos

cada milisegundo simulado. Evidentemente, incrementar la frecuencia llevará a tener un modelo más preciso, pero también incrementará el costo de la simulación de forma significativa. Los resultados esperados para ambos casos se presentan en la Fig. 5.

Figura 5: Gráficas de la disipación de potencia en el CPU0 del clúster "big." En este caso solo se muestra la disipación durante el arranque del sistema simulado.

Note que los modelos de potencia utilizados corresponden con el cálculo de la potencia dinámica y estática del microprocesador. En el modelo propuesto el primero de estos valores corresponde a dos veces el voltaje del núcleo multiplicado por el número de instrucciones por ciclo. Para el segundo se toma cuatro veces la temperatura del procesador. Existen tres valores globales que se pueden utilizar en estos modelos: el voltaje (voltage), la temperatura (temp) y el periodo del procesador (clock\_period). Fuera de estos, para hacer uso de otras estadísticas se debe proporcionar el nombre completo del objeto, por ejemplo, la siguiente expresión va a representar el número de instrucciones por ciclo para el procesador inmediatamente asociado con el modelo:

```

"{}.ipc".format(cpu_path)

```

Este tipo de asignación dinámica permitirá poder utilizar un modelo genérico que se aplicará a todos los objetos de tipo CPU o que tienen relación con un CPU.

# V-C. Aplicaciones y checkpoints

Una vez que se tiene una simulación aproximada de la arquitectura de interés, el siguiente paso será poder modificar las aplicaciones que se desea ejecutar dentro del sistema. En el ejemplo propuesto se usa Ubuntu como sistema operativo, y éste usa el sistema de archivos contenido dentro de un disco. Por ende, una forma sencilla de proceder es primero crear las aplicaciones, posteriormente compilarlas, y finalmente cargarlas en el archivo de disco.

Para crear una aplicación o programa es posible escribirla en prácticamente cualquier lenguaje de programación y después usar una serie de intérpretes y compiladores que permitirán crear el código objeto para la arquitectura que deberá ejecutar este software. En este caso se partirá de una especificación en lenguaje C, que es popularmente utilizado en procesos de formación por su eficiencia y disponibilidad:

```

#include <stdio.h>

int main()

{

printf("Hello World from gem5!\n");

return 0;

}

```

Normalmente, el siguiente paso sería compilar el programa y ejecutarlo. Sin embargo, se debe tener en cuenta que, al utilizar un compilador instalado en el ordenador de trabajo, este creará un código para la arquitectura de dicho ordenador. Por ende, es necesario utilizar un compilador cruzado o *cross-compiler* que permitirá generar un archivo ejecutable por la arquitectura de interés, en este caso ARM.

Existe una amplia variedad de compiladores para ARM [17] que pueden ser utilizados según el entorno de trabajo de la plataforma. Para el ejemplo propuesto se utilizará la herramienta aarch64-none-linux-gnu-gcc que permite compilar un código C para una arquitectura AArch64 con Linux. Su uso es bastante intuitivo:

```

wget https://developer.arm.com/-/media/Files/downloads/

gnu-a/10.3-2021.07/binrel/gcc-arm-10.3-2021.07-

x86_64-aarch64-none-linux-gnu.tar.xz

tar -xf gcc-arm-10.3-2021.07-x86_64-aarch64-none-linux-

gnu.tar.xz

mv gcc-arm-10.3-2021.07-x86_64-aarch64-none-linux-gnu

toolchain

./toolchain/bin/aarch64-none-linux-gnu-gcc hello.c -o

hello

```

En seguida se cargará la aplicación en formato binario en el sistema de archivos de Ubuntu a emular. Para ello es necesario *montar* el disco y copiar el archivo. El proceso es un poco complejo, pero repetitivo. Una vez que se comprende la secuencia de pasos la tarea resulta sencilla:

Note que en este paso se requieren permisos de administrador para montar y copiar al disco que se busca emular. La aplicación por ejecutar estará disponible en /home.

Evidentemente, si el objetivo principal de un experimento es editar el archivo binario que se ha creado, no será del todo atractivo el tener que simular todo el arranque del sistema operativo con cada modificación. Para ello se puede hacer uso de la instrucción m5 checkpoint dentro de la simulación. Posteriormente se puede hacer uso del argumento --restore-from para especificar la ruta del punto de restauración deseado. Note que el número asociado con el punto de restauración es asignado de forma dinámica.

```

./build/ARM/gem5.opt \

./configs/example/arm/Hikey960.py \

--big-cpus 4 \

--little-cpus 4 \

--cpu-type=timing \

--caches \

--dtb=./system/arm/dt/

armv8\_gem5\_v1\_big\_little\_4\_4.dtb \ \backslash

--bootloader=./common/binaries/boot.arm64 \

--kernel=./common/binaries/vmlinux.arm64 \

--disk=./common/ubuntu-18.04-arm64-docker.img \

--dvfs \

--big-cpu-clock 2362MHz 2112MHz 1805MHz 1421MHz

903MHz \

--little-cpu-clock 1402MHz 999MHz 533MHz \

--big-cpu-voltage 1.0V 0.99V 0.98V 0.97V 0.96V \

--little-cpu-voltage 0.87V 0.86V 0.85V \

--power-models \

--stat-freq 1.0E-3 \

--restore-from=./m5out/cpt.1044789997495

```

Y con esto finalizamos la demostración del uso de *gem5* para emular un procesador moderno con algunas características prácticas. Los archivos fuente generados o editados se pueden encontrar en [18]. Otras fuentes sobre el uso de *gem5* para emular las características físicas de procesadores pueden consultarse en [19], [20].

## VI. Conclusión

En este artículo hemos analizado uno de los retos que se pueden encontrar en los procesos de formación de estudiantes de educación superior y posgrado. Hablamos de la dificultad por tener acceso a sistemas de evaluación y prototipados modernos, que les permitan adquirir experiencia con las nuevas tecnologías utilizadas en la industria o la investigación.

Hemos descrito herramientas usadas para estudiar sistemas digitales y enumerado los problemas que existen con las soluciones conocidas. Concluyendo que emular un sistema de cómputo requiere una reproducción de su comportamiento lógico y la estimación de diversos indicadores sobre su operación. El simulador gem5 ofrece ambas opciones.

Esta herramienta es un software de código libre y de distribución gratuita que puede ser empleada para emular sistemas de cómputo modernos como los que se basan en procesadores ARM y RISC-V. Permite verificar la operación no solo de los programas que se han de ejecutar sobre el sistema simulado y proporciona datos adicionales que pueden ser de interés para el análisis de un chip.

No obstante, existen tres retos principales para poder considerar a gem5 como una solución de aplicación práctica, en particular para el caso de Latinoamérica. Primero, la complexidad del software obliga a utilizar sistemas de cómputo potentes que a menudo no serían disponibles para los estudiantes de recursos limitados. Segundo, gem5 solo funciona para sistemas Linux que no son ampliamente conocidos. Y finalmente, tiene una curva de aprendizaje muy lenta. Nuestro trabajo trata de abordar este último desafío.

#### RECONOCIMIENTOS

Los autores reconocen el financiamiento de la *Agence Nationale de la Recherche (ANR)*—Francia—a través del proyecto ARCHI-SEC (ANR-19-CE39-0008).

#### REFERENCIAS

- J. M. Munera, A. Jimenez, M. A. Botero, K. Y. Rivas, and J. Lopez, "La educación moderna al alcance de arduino," *Revista ESPACIOS*, vol. 798, p. 1015, 2020.

- [2] I. H. P. Tavera et al., "Arduino en el nivel medio superior," Vida Científica Boletín Científico de la Escuela Preparatoria No. 4, vol. 11, no. 22, pp. 10–11, 2023.

- [3] J. C. Moreno-Brid and P. Ruiz-Nápoles, "La educación superior y el desarrollo económico en América Latina," Revista iberoamericana de educación superior, vol. 1, no. 1, pp. 171–188, 2010.

- [4] H. K. Kondaveeti, N. K. Kumaravelu, S. D. Vanambathina, S. E. Mathe, and S. Vappangi, "A systematic literature review on prototyping with Arduino: Applications, challenges, advantages, and limitations," *Computer Science Review*, vol. 40, p. 100364, 2021.

- [5] M. El-Abd, "A review of embedded systems education in the Arduino age: Lessons learned and future directions," *International Journal of Engineering Pedagogy*, vol. 7, no. 2, pp. 79–93, 2017.

- [6] A. Chakraborty, "Global Semiconductor Shortage Triggering Obstructions and Production Delays," Ph.D. dissertation, Swiss School of Business and Management Geneva, Switzerland, 2023.

- [7] J. Voas, N. Kshetri, and J. F. DeFranco, "Scarcity and global insecurity: The semiconductor shortage," *IT Professional*, vol. 23, no. 5, pp. 78–82, 2021.

- [8] Á. Guerra Martín, "Aplicación Android para simular una FPGA educativa," Universidad Autónoma de Madrid, Trabajo Final de Grado, 2013

- [9] S. R. Yesa, J. García-Zubía, J. L. G. Temiño, J. V. Sáez, and I. A. Martínez, "Uso de un laboratorio remoto de FPGAs para la realización de prácticas en grados de ingeniería," in XIV Congreso de Tecnologías Aplicadas a la Enseñanza de la Electrónica. Instituto Superior de Engenharia do Porto, 2020, pp. 293–300.

- [10] F. Bellard, "QEMU, a Fast and Portable Dynamic Translator," in Proceedings of the Annual Conference on USENIX Annual Technical Conference, ser. ATEC '05. USA: USENIX Association, 2005, p. 41.

- [11] A. Vladimirescu, The Spice Book. USA: John Wiley & Sons, Inc., 1994.

- [12] M. M. K. Martin, D. J. Sorin, B. M. Beckmann, M. R. Marty, M. Xu, A. R. Alameldeen, K. E. Moore, M. D. Hill, and D. A. Wood, "Multifacet's General Execution-Driven Multiprocessor Simulator (GEMS) Toolset," SIGARCH Comput. Archit. News, vol. 33, no. 4, p. 92–99, nov 2005.

- [13] N. L. Binkert, R. G. Dreslinski, L. R. Hsu, K. T. Lim, A. G. Saidi, and S. K. Reinhardt, "The M5 Simulator: Modeling Networked Systems," *IEEE Micro*, vol. 26, no. 4, p. 52–60, jul 2006.

- [14] N. Binkert, B. Beckmann, G. Black, S. K. Reinhardt, A. Saidi, A. Basu, J. Hestness, D. R. Hower, T. Krishna, S. Sardashti, R. Sen, K. Sewell, M. Shoaib, N. Vaish, M. D. Hill, and D. A. Wood, "The Gem5 Simulator," SIGARCH Comput. Archit. News, vol. 39, no. 2, p. 1–7, aug 2011.

- [15] Statcounter, "Web Analytics Made Easier Statcounter," https:// statcounter.com/, 2024, [Online; accessed 14-May-2024].

- [16] gem5, "Building gem5," https://www.gem5.org/documentation/general\_docs/building, 2024, [Online; accessed 14-May-2024].

- [17] Arm, "Downloads Arm Developer," https://developer.arm.com/downloads, 2024, [Online; accessed 14-May-2024].

- [18] C. A. Lara-Nino, "Clock and Power management on Gem5," https://github.com/CarlosAndresLARA/hikey960-gem5, 2024, [Online; accessed 14-May-2024].

- [19] L. Bossuet and C. A. Lara-Nino, "Emulating Covert Data Transmission on Heterogeneous SoCs," in 2023 Asian Hardware Oriented Security and Trust Symposium (AsianHOST), 2023, pp. 1–6.

- [20] L. Bossuet, V. Grosso, and C. A. Lara-Nino, "Emulating Side Channel Attacks on gem5: lessons learned," in 2023 IEEE European Symposium on Security and Privacy Workshops (EuroS&PW), 2023, pp. 287–295.